# Comprehensive Review On To Study about Analyses of Harmonic Mitigation Using Cascaded H-Bridge

Mrs. Payal P Raval, Mrs. Rohini Iiyer K

Lecture, Electrical Department,

R.C. Polytechnic Institute, Ahmedabad, Gujarat, India

Abstract - Recent years Multilevel inverters have been growing attention mainly in the distributed energy resources area due to several batteries, solar cell, fuel cells, wind and micro turbines can be connected through multilevel inverter to supply a load or the ac grid. Multilevel inverter work as an alternative in the area of high power medium-voltage energy control. So, Harmonic mitigation in multi level inverters are measured very important task. For mitigate the harmonics researchers have lot suggested modifications in the circuit topology and optimal firing selection angle using nonconventional and conventional optimization algorithms. This paper presents a review of application by different multilevel inverter techniques for harmonic reduction.

Keyword - Cascaded Multilevel Inverter, H-bridge, Multilevel Inverter, Total Harmonic Distortion (THD).

### **I.INTRODUCTION**

Various industrial applications have begun to require high power apparatus in recent years like several medium voltage motor drives; usefulness applications require medium voltage and megawatt power level. Used for a medium voltage grid, it is difficult to connect only one power semiconductor switch directly. Then a multilevel power inverter arrangement has been introduced while an alternative in high power and medium voltage situations. A multilevel inverter is not only achieves high power ratings but also implement the use of renewable energy sources. Renewable energy sources such as wind, photovoltaic and fuel cells can be easily combined to a multilevel converter system for a high power application.

Basically the concept of multilevel inverters has been introduced since 1975[3]. The word multilevel appears with the three level inverters [1]. Then, numerous multilevel inverter topologies have been developed. Though, multilevel inverter elementary concept to achieve higher power is to use of power semiconductor switches series with several lower voltages dc sources to perform the power conversion by synthesizing a staircase voltage waveform. Batteries, Capacitors and renewable energy voltage sources can be used as the multiple dc sources in order to achieve high voltage at the output; conversely, the power semiconductor switches rated voltage depends only upon the rating of the dc voltage sources to which they are connected.

Generally inverters convert DC power into AC power through waves called sine waves or modified sine waves. Modified sine waves are prepared to simulate sine waves. Sine waves are the waves that are typically found in power from a power plant. Now consider inverters with modified sine waves work well for backup power in houses and are economically. Even if there are numerous types of inverters, all standard inverters use only one switch, or in other words, one power circuit.

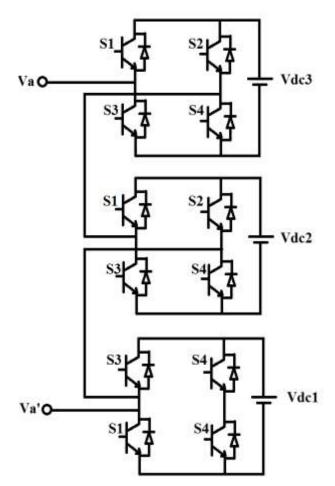

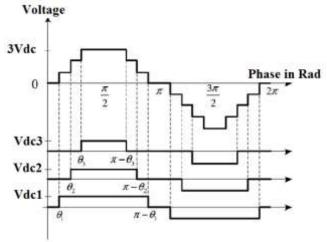

# II.CASCADED H-BRIDGE MULTILEVEL INVERTER

The cascaded multilevel inverter made of a series of H bridge (single-phase full-bridge) inverter units. Every full-bridge can produce three different voltage outputs like -Vdc, 0, and +Vdc. Though, three multilevel inverters can produce staircase waveform as shown in Figure 1. The numeral of output phase voltage levels in a cascaded multilevel inverter equation is 2S + 1, here S is the number of dc sources. Consider the case, if phase voltage waveform for a 7-level cascaded multilevel inverter with three isolated dc sources is shown in Figure 2. Every H-bridge module generates a quasi-square waveform by phase-shifting the switching timings of its positive and negative phase legs.

Generally there are three structures for multilevel inverters:

(1) Cascaded H-Bridges:

In Figure 1.1, each DC power source is connected to an H-bridge inverter. Basically the single inverter has four switches. By using switching combinations, the single inverter can create three different AC voltage outputs.

Figure 1 Basic Diagram of three level Cascaded Inverter

Figure 2 The Output waveform of a 3 level inverter

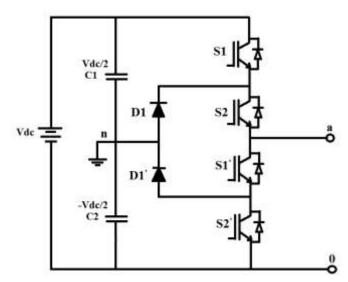

# (2) Diode-Clamped Multilevel Inverter:

The second one is Diode-clamp multi inverter, this type of inverter is appropriate for transmission of DC current on an AC transmission line. Accurate control and monitoring are required to prevent overcharging or discharging.

Figure 3 Basic Circuit Diagram of three level diode-clamped inverter

Illustrate in figure 3, here the dc bus voltage is opening into three levels by two series-connected bulk capacitors  $C_1$  and  $C_2$ . The two capacitors middle point 'n' can be specified as the neutral point. Here the output voltage  $V_{an}$  has three states:  $-V_{dc}/2$ , 0,  $+V_{dc}/2$ . Now consider, for voltage level  $V_{dc}/2$  at that time switches  $S_1$  and  $S_2$  need to be turned on and for  $-V_{dc}/2$  at that time switches  $S_1$ ' and  $S_2$ 'need to be turned on; and forthe 0 level,  $S_2$  and  $S_1$ ' need to be turned on.

In this method the key components that distinguish this circuit from a usual two-level inverter are  $D_1$  and  $D_1$ . These two diodes clamp the switch voltage to half the level of the dc-bus voltage. When both switches  $S_1$  and  $S_2$  turn on, the voltage across a and 0 is  $V_{dc}$  specially when  $V_{ao}$ =  $V_{dc}$ . In this concision, diode  $D_1$ ' is balances out which the voltage sharing between  $S_1$ ' and  $S_2$ ' with  $S_1$ ' blocking the voltage across it and blocking the voltage across  $C_1$  and  $C_2$  blocking the voltage across  $C_2$ . Note that output voltage  $C_3$  and  $C_4$  is dc. The variation between  $C_4$  and  $C_4$  and  $C_4$  are voltage across  $C_4$  which is  $C_4$  and  $C_4$  condition the output is removed between  $C_4$  and  $C_4$  and  $C_4$  and  $C_4$  are voltage levels:  $C_4$  and  $C_4$  and  $C_4$  and  $C_4$  are voltage across  $C_4$  and  $C_4$  and  $C_4$  are voltage levels:  $C_4$  and  $C_4$  and  $C_4$  are voltage levels:  $C_4$  and  $C_4$  and  $C_4$  are voltage levels:  $C_4$  are voltage levels:  $C_4$  and  $C_4$  are voltage levels:  $C_4$  and  $C_4$  are voltage levels:  $C_4$  are voltage levels:  $C_4$  and  $C_4$  are voltage levels:  $C_4$  are voltage levels:  $C_4$  and C

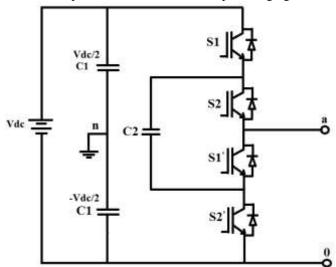

(3) Capacitor-Clamped Multilevel Inverter:

The third one is Capacitor-Clamped multilevel inverter, which has a similar design to a diode-clamped inverter. Though, the clamping diodes have been replaced with capacitors. I this inverter design required only two switch combinations to create a output voltage. Finding the output of all the capacitors is difficult, since is pre-charging all of the capacitors [1].

Figure 4 Circuit Diagram of Three level Capacitor – clamped inverter

Illustrates figure 4 the basic building block diagram of a phase-leg capacitor-clamped inverter. This circuit has been called the flying capacitor inverter with autonomous capacitors clamping the device voltage to one capacitor voltage level. The inverter in Figure 4 provides a three-level output across a and n, i.e.,  $V_{an}$ = - $V_{dc}$ /2, 0, or  $V_{dc}$ /2. For voltage level  $V_{dc}$ /2, in this case switches  $S_1$  and  $S_2$  need to be turned on and for - $V_{dc}$ /2, in this case switches  $S_1$ ' and  $S_2$ ' need to be turned on; and if the 0 level, either pair ( $S_1$ , $S_1$ ') or ( $S_2$ , $S_2$ ') needs to be turned on. Clamping capacitor  $C_1$  is charged when  $S_1$  and  $S_1$ ' are turned on, and is discharged when  $S_2$  and  $S_2$ ' are turned on. Now the charge capacitor  $C_1$ can be balanced by appropriate selection of the 0-level switch combination.

# III.FLEXIBILITY OF ELECTRIC POWER TRANSMISSION

The capability to control of changes in the electric transmission system while maintaining enough steady-state and transient boundaries.

Based on a PE (power electronic) system and other static apparatus that implemented to control of more than one AC transmission system parameters to improve controllability and raise power transfer ability [6].

Through the advancement of semi-conductor devices, essentially the devices with turn-off capability, the outlay of FACTS device technology day by day to decrease, and this will formulate the FACTS device technology is more reliable. The increase of FACTS controlling devises has basically followed two specifically different technical approaches, both approaches have resulting in a comprehensive controllers group that solves some of the transmission problems. In the first technical group is based on thyristor devices by only gate turn-on and turn-off depends on the current getting zero value as per circuit and system conditions. Controllers in this type of group utilize reactive with thyristor switches as controlled elements.

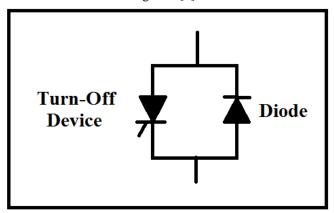

Now consider the other group, in this group devices like MTO (MOS turn-off thyristors), gate turn-off thyristor (GTO), and integrated gate-commutated thyristors (IGCT), and other similar devices that have turn –on and turn-off capability. This type of group uses self-commutating static converters operation like controlled source voltages for FACTS applications [8]. Although DC current in a VSC (voltage-sourced converter) flows in any direction, the converter valve have to be bi-directional, and also, as the dc voltage does not repeal then the turn-off devices does not need to reverse voltage ability; such turn-off devices are identified as asymmetric turn-off devices. Accordingly, a SVC (source voltage converter) is made up of an asymmetric turn-off device like GTO with a parallel diode connected in reverse as seen in Figure 5 [7].

Figure: 5 Diode Arrangement for a voltage-sourced converter

### IV.SELECTIVE HARMONIC ELIMINATION

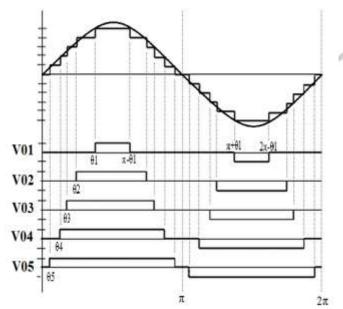

Generally a 7-level inverter waveform illustrate in figure 7 has three variables (as:  $\theta$ 1,  $\theta$ 2, and  $\theta$ 3). Allowing for the same amplitude of all dc sources, the development of the Fourier series the output voltage waveform is illustrate in Figure 7.

## V.ASYMMETRICAL CASCADED MLI (MULTI LEVEL INVERTER)

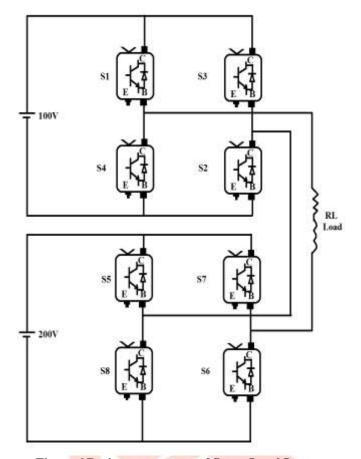

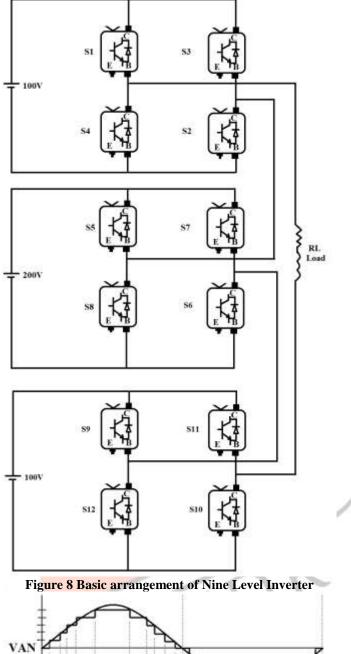

Moreover Asymmetric Cascaded Multilevel Inverter has unequal DC sources magnitude of voltage is used in [5]. At this time 7 level and 9 levels Asymmetric Cascaded MLI is analyzed [2]. Consider the case of 7 level ACMI (Asymmetric Cascaded multilevel inverter), there are two asymmetrical magnitude DC sources and 8 power switches are used and consider other case of 9 level ACM (Asymmetric Cascaded multilevel), three DC sources are used having 2 same sources and three different sources and also 12 power switches are used. The basic circuit diagrams of 7 levels and 9 levels ACMLI are illustrate in figure 6 and 8 respectively.

Figure 6 Basic arrangement of Seven Level Inverter

Figure 7 Waveform of the seven level Inverter

VAN

VO1

01

02

VO3

VO4

03

VO4

04

VO5

05

Figure 9 Waveform of the Nine level Inverter

Now the Asymmetrical cascaded 9 level inverter has three DC sources and twelve power switches, magnitude of DC sources are 100V, 200V and 100V respectively [4]. The sources are connected to three H-Bridge units which are cascaded in single phase and output voltage of an individual H-bridge is -VDC, 0 or +VDC. To obtain the preferred output voltage the power switches are turned OFF and ON. Through the formation of the proper switches combination we obtain the desired output voltage. To reach maximum output voltage; the switches S1, S10, S9, S6, S5 and S2 are ON and other switches are remaining OFF at that time. If consider other case, output voltage is +3V; the switches S1, S10, S12, S6, S5 and S2 are ON and other remaining are OFF.

# **VI.CONCLUSION**

Voltage source inverter (VSI) that synthesize the inverter voltage by equally divided capacitor voltages. The application on which the multilevel voltage source inverter may have the most impact is the adjustable speed drive. The recently industry reported numerous ASD bearing failures and winding insulation breakdowns due to high switching frequency PWM inverters. Using multilevel inverters not only solves harmonics and EM1 problems, but its also avoids possible high frequency switching *dvldt* induced motor failures.

Among a balanced voltage stress in devices and utility compatible features, the multilevel inverters have shed a light in the power electronics ground and are rising as a new breed of power inverters for high-voltage high-power applications. From the study of this paper it is clear to under stand that when the inverter level is increased at that time we get the desired sine wave.

## VII. REFERENCES

- [1] Jose Rodriguez, Jih-Sheng Lai and Fang Zheng Peng, "Multilevel Inverters: A Survey of Topologies, Controls, and Applications", IEEE Transactions, OnIndustrial Electronics, No. 4, Vol. 49, August 2002.

- [2] Bharath. K, R. J. Satputaley, "Single phase Asymmetrical Cascaded Multilevel Inverter Design for Induction Motor", ASAR-International Conference, ISBN:978-81-927147-0-7.

- [3] L.H. Bannister and R. H. Baker, "Electric power converters", U.S. Patent 3 867 643, Feb 1975.

- [4] Phee Kuan Jin, Christian Klumpner and Mohamed S.A.Dahidah, "Nine-Level SHE-PWM VSC Based STATCOM for VAR Compensation", IEEE International Conference on Power and Energy, Nov-Dec 2010.

- [5] Wanki Min, Jaeho Choi and Joonki Min, "Control of STATCOM Using Cascade Multilevel Inverter for High Power Application", IEEE International Conference on Power Electronics and Drive Systems, PEDS, July 1999, Hong Kong.

- [6] Jose Rodriguez, Fang Zheng Peng and Jih-Sheng Lai, "Multilevel Inverters: A Survey of Topologies, Controls, and Applications", IEEE Transactions on Industrial Electronics, 49(4), ISBN: 2002, 724-738

- [7] T. Manokaran, B. Sakthivel and S. Mohamed Yousuf, "Cascaded Multilevel Inverter based Harmonic Reduction in STATCOM", International Journal of Engineering Science and Technology, ISBN: 5424-5431, 2010.

- [8] P.S. Bimbhra, "Power Electronics", Khanna publishers, New Delhi, ISBN-81-7409-056-8.