# SIMULATION AND IMPLEMENTATION OF MULTILEVEL INVERTER BASED INDUCTION MOTOR DRIVE BASED ON PWM TECHNIQUES

<sup>1</sup>CH.Manasa, <sup>2</sup>K.Uma, <sup>3</sup>D.Bhayana

Students of B.Tech, Electrical and Electronics Department BRECW, JNTUH, Telangana. Under the guidance of Racharla Manju Bhargavi, Associate Professor, Department of EEE, BRECW, JNTUH, India, manju.racharla@gmail.com

Abstract — The main objective of this paper is to control the speed of an induction motor by using five level diode clamped multilevel inverter. To obtain high quality sinusoidal output voltage with reduced harmonics, multicarrier PWM control scheme is proposed for diode clamped multilevel inverter. An open loop speed control can be achieved by using V/f method. This method can be implemented by change the supply voltage and frequency applied to the three phase induction motor at constant ratio. The proposed system is an effective replacement for the conventional method which produces high switching losses, results in poor drive performance. The simulation results reveal that the proposed circuit effectively controls the motor speed and enhances the drive performance through reduction in total harmonic distortion (THD).

**Keywords** — Diode clamped multilevel inverter, Induction motor, Multicarrier PWM technique, THD, V/f method.

### I. INTRODUCTION

Majority of industrial drives use ac induction motor because these motors are rugged, reliable, and relatively inexpensive. Induction motors are mainly used for constant speed applications because of unavailability of the variable-frequency supply voltage. But many applications need variable speed operations. Historically, mechanical gear systems were used to obtain variable speed. Recently, power electronics and control systems have matured to allow these components to be used for motor control in place of mechanical gears. These electronics not only control the motor's speed, but can improve the motor's dynamic and steady state characteristics. Adjustable speed ac machine system is equipped with an adjustable frequency drive that is a power electronic device for speed control of an electric machine. It controls the speed of the electric machine by converting the fixed voltage and frequency to adjustable values on the machine side.

High power induction motor drives using classical three phase converters have the disadvantages of poor voltage and current qualities. To improve these values, the switching frequency has to be raised which causes additional switching losses. Another possibility is to put a motor input filter between the converter and motor, which causes additional weight. A further inconvenience is the limited voltage that can be applied to the induction motor determined by inconvenience is the limited voltage that can be applied to the induction motor determined by the blocking voltage of the semiconductor switches. The concept of multilevel inverter control has opened a new possibility that induction motors can be controlled to achieve dynamic performance equally as that of dc motors. Recently many schemes have been developed to achieve multilevel voltage profile, particularly suitable for induction motor drive applications. The diode clamp method can be applied to higher level converters. As the number of level increases, the synthesized output waveform adds more steps, producing a staircase waveform. A zero harmonic distortion of the output wave can be obtained by an infinite number of levels. Unfortunately, the number of the achievable levels is quite limited not only due to voltage unbalance problems but also due to voltage clamping requirement, circuit layout and packaging constraints.

In this paper, a three-phase diode clamped multilevel inverter fed induction motor is described. The diode clamped inverter provides multiple voltage levels from a series bank of capacitors. The voltage across the switches has only half of the dc bus voltage. These features effectively double the power rating of voltage source inverter for a given semiconductor device. The proposed inverter can reduce the harmonic contents by using multicarrier PWM technique. It generates motor currents of high quality. V/f is an efficient method for speed control in open loop.

In this scheme, the speed of induction machine is controlled by the adjustable magnitude of stator voltages and its frequency in such a way that the air gap flux is always maintained at the desired value at the steady-state. Here the speed of an induction motor is precisely controlled by using three level diode clamped multilevel inverter.

## II. CONVENTIONAL METHOD

The voltage source inverter produces an output voltage or a current levels can be zero or  $\pm Vdc/2$  or  $\pm Vdc$ . This is known as three level inverter. To obtain the quality output voltage or a current waveform with a minimum amount of ripple content, it requires high switching frequency along with various pulse width modulation strategies. In high-power and high voltage applications, these three-level inverters have some limitations in operating at high frequency mainly due to switching losses and constraints of device ratings. The dc link voltage of a three-level Inverter is limited by voltage ratings of switching devices; the problematic series connection of switching devices is required to raise the dc link voltage.

By series connection, the maximum allowable switching frequency has to be more lowered; hence the harmonic reduction becomes more difficult. In addition, the three level inverters generate high frequency common-mode voltage within the motor windings which may result in motor and drive application problems.

Figure 1: Three level Inverter

From the aspect of harmonic reduction and high dc link voltage level, three-level approach seems to be the most promising alternative. The harmonic contents of a three-level inverter are less than that of a two-level inverter at the same switching frequency and the blocking voltage of the switching device is half of the dc-link voltage. A three level inverter will not generate common-mode voltages when the inverter output voltages are limited within certain of the available switching states. So the three level inverter topology is generally used in realizing the high performance, high voltage ac drive systems.

## III. DRIVE SYSYEM DESCRIPTION

In the conventional technique normal PWM method is used. So that the voltage and current is of poor qualities and the switching frequency causes more amount of switching losses. Those drawbacks are rectified using three phase diode clamped multilevel inverter.

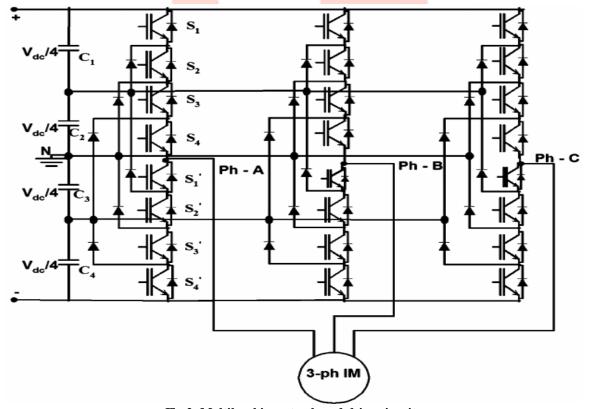

Structure of five Level Diode Clamped Multilevel Inverter:

Fig.2. Multile vel inverter based drive circuit

The voltage and current quality are better and the switching losses are reduced when compared to the conventional technique. Also the THD is found to be better.

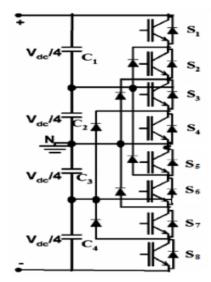

Single leg Diagram of Five level inverter

The five-level neutral point-clamped voltage source inverter is shown in Fig.2. It contains 24 unidirectional active switches and 18 neutral point clamping diodes. The middle point of the four capacitors "n" can be defined as the neutral point. The major benefit of this configuration is each switch must block only one-fourth of the dc link voltage (Vdc/4). In order to produce five levels, only four of the eight switches in each phase leg should be turned on at any time. The dc-bus voltage is split into five levels by four series-connected bulk capacitors, C1, C2, C3 and C4 they are same in rating. For DC bus voltage Vdc, the voltage across each capacitor is Vdc/4 and each device voltage stress will be limited to one capacitor voltage levels Vdc/4 through clamping diodes. The diodes are all same type to provide equal voltage sharing and to clamp the same voltage level across the switch, when the switch is in off condition. Hence this structure provides less voltage stress across the switch.

### IV. PRINCIPLE OF OPERATION

To produce a staircase-output voltage, consider one leg of the three-level inverter, as shown in Fig.3. The steps to synthesize the three-level voltages are as follows.

- a. For voltage levels Van= Vdc/2 turn on all upper switches S1-S4.

- b. For voltage level Van= Vdc/4, turn on three upper switches S2-S4 and lower switch S5

- c. For voltage level Van=0, turn on two upper switches S3 and S4 and two lower switches S5 and S6.

- d. For voltage levels Van = -Vdc/4, turn on one upper switch S4 and three lower switches S5-S7.

- e. For voltage levels Van=-Vdc/2, turn on all lower switches S5-S8.

NPC inverter which has been extensively used today in industrial drives, traction as well as FACT's system Based on concept of using diodes to limit power devices voltage stress Output phase voltage can assume any voltage level by selecting any of the nodes.

$$V_{dc}/2 , V_{ref,i} > V_{tri,1}$$

$$V_{dc}/4 , V_{ref,i} > V_{tri,2}$$

$$0 , V_{tri2} > V_{ref,i} > V_{tri,3}$$

$$-V_{dc}/4 , V_{tri,3} > V_{ref,i}$$

$$-V_{dc}/2 , V_{tri,4} > V_{ref,i}$$

Table.1. shows the voltage levels and their corresponding switch states. State condition 1 means the switch is on, 0 means the switch is off. There are two complementary switch pairs in each phase.

These pairs for one leg of the inverter are (S1, S5), (S2, S6), (S3, S7), (S4, S8). If one of the complementary switch pairs is turned on, the other of the same pair must be off.

TABLE 1 Output voltage levels and their Switching states.

| OUTPUT<br>VOLTAGES  | S1 | S2 | 83 | S4 | S5 | S6 | <b>S</b> 7 | SS |

|---------------------|----|----|----|----|----|----|------------|----|

| V <sub>dc</sub> /2  | 1  | 1  | 1  | 1  | 0  | 0  | 0          | 0  |

| $V_{ m dc}/4$       | o  | 1  | 1  | 1  | 1  | 0  | 0          | О  |

| o                   | 0  | 0  | 1  | 1  | 1  | 1  | 0          | 0  |

| -V <sub>de</sub> /4 | 0  | 0  | 0  | 1  | 1  | 1  | 1          | 0  |

| -V <sub>dc</sub> /2 | 0  | 0  | 0  | 0  | 1  | 1  | 1          | 1  |

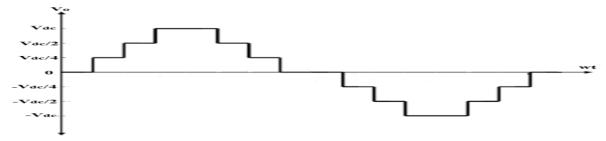

Fig.4. shows the phase voltage waveform of the three-level inverter. The m-level converter has an m-level output phase-leg voltage and a (2m-1)-level output line voltage.

Fig.4. Three level inverter output voltage.

The most attractive features of multilevel inverters are as follows.

- a. They can generate output voltages with extremely low distortion and lower dv/dt.

- b. They draw input current with very low distortion.

- c. They generate smaller common-mode (CM) voltage, thus reducing the stress in the motor bearings.

- d. They can operate with a lower switching frequency.

## V. PROPOSED SCHEME

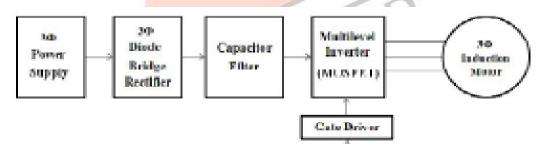

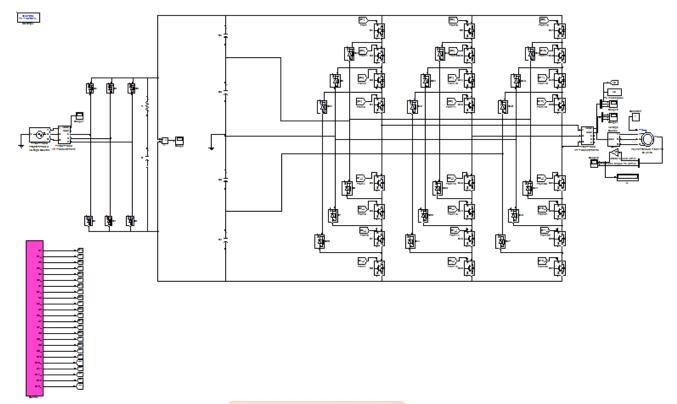

The block schematic of multilevel inverter fed three phase induction motor is as shown in Fig.5. The complete system will consist of two sections; a power circuit and a control circuit. The power section consists of a power rectifier, filter capacitor, and three phase diode clamped multilevel inverter. The motor is connected to the multilevel inverter. An ac input voltage is fed to a three phase diode bridge rectifier, in order to produce dc output voltage across a capacitor filter. A capacitor filter, removes the ripple contents present in the dc output voltage. The pure dc voltage is applied to the three phase multilevel inverter through capacitor filter. The multilevel inverter has 24 IGBT switches that are controlled in order to generate an ac output voltage from the dc input voltage. The control circuit of the proposed system mainly consists of gate driver circuit. Here Multicarrier PWM technique is used for the production of gate pulses to the IGBT switches. The output ac voltage is obtained from the multilevel inverter can be controlled in both magnitude and frequency (V/f open loop control). The controlled ac output voltage is fed to the induction motor drive. When the power switches are on, current flows from the dc bus to the motor winding. The motor windings are highly inductive in nature; they hold electric energy in the form of current. This current needs to be dissipated while switches are off. Diodes are connected across the switches give a path for the current to dissipate when the switches are off. These diodes are also called freewheeling diodes. The V/f control method permits the user to control the speed of an induction motor at different rates. For continuously variable speed operation, the output frequency of multilevel inverter must be varied. The applied voltage to the motor must also be varied in linear proportion to the supply frequency to maintain constant motor flux.

Fig.5. Basic block diagram

# VI. MODULATION STRATEGY

This Paper mainly focuses on multicarrier PWM method. This method is simple and more flexible than SVM methods. The multicarrier PWM method uses several triangular carrier signals, keeping only one modulating sinusoidal signal. If an n-level inverter is employed, n-1 carriers will be needed. The carriers have the same frequency WC and the same peak to peak amplitude Ac and are disposed so that the bands they occupy are contiguous. The zero reference is placed in the middle of the carrier set. The modulating signal is a sinusoidal signal of frequency Wm and amplitude Am. At every instant each carrier is compared with the modulating signal. Each comparison gives 1(-1) and 2(-2), if the modulating signal is greater than the triangular carrier signal then the pulse is produced. The results are added to give the voltage level, which is required at the output terminal of the inverter. Multicarrier PWM method can be categorized into two groups:

1) Carrier Disposition (CD) method 2) Phase shifted PWM method.

Advantages of multicarrier PWM techniques:

- a. Easily extensible to high number of levels.

- b. Easy to implement.

- c. To distribute the switching signals correctly in order to minimize the switching losses.

- d. To compensate unbalanced dc sources.

Related to the way the carrier waves are placed in relation to the reference signal, three cases can be distinguished:

- Alternative Phase Opposition Disposition (APOD), where each carrier band is shifted by 180° from the adjacent bands.

- Phase Opposition Disposition (POD), where the carriers above the zero reference are in phase, but shifted by 180° from those carriers below the zero reference.

- In-Phase Disposition (PD), where all the carriers are in phase. In this paper the gating pulses for MOSFET switches are generated by using In-phase disposition technique.

In this paper the gating pulses for IGBT switches are generated by using In-phase disposition technique.

Fig.6. In-phase disposition technique

# VII. V/f CONTROL THEORY

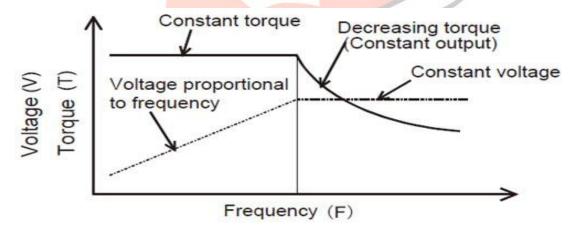

Fig. 7. shows the relation between the voltage and torque versus frequency. The voltage and frequency being increased up to the base speed. At base speed, the voltage and frequency reach the rated values. We can drive the motor beyond base speed by increasing the frequency further. But the voltage applied cannot be increased beyond the rated voltage.

Therefore, only the frequency can be increased, which results in the field weakening and the torque available being reduced. Above base speed, the factors governing torque become complex, since friction and wind age losses increase significantly at higher speeds.

Hence, the torque curve becomes nonlinear with respect to speed or frequency.

Fig.7. Speed-Torque characteristics with V/f control

## VIII. SIMULATED CIRCUITS AND WAVEFORMS

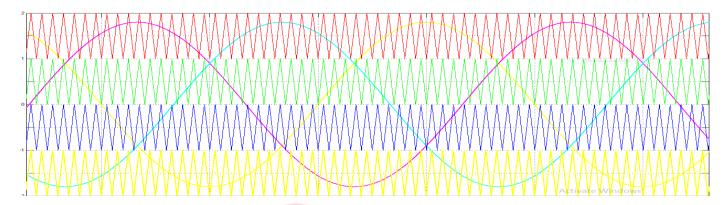

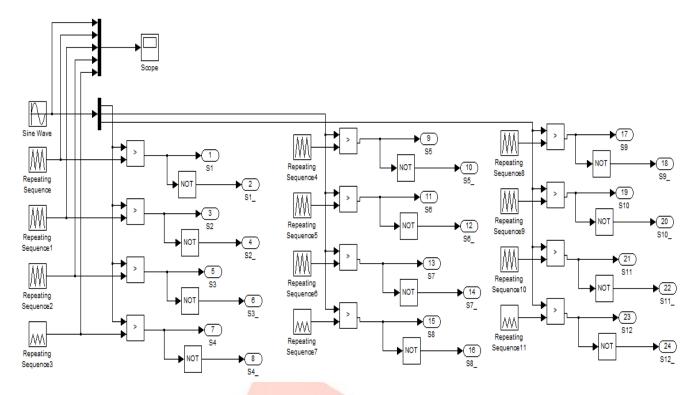

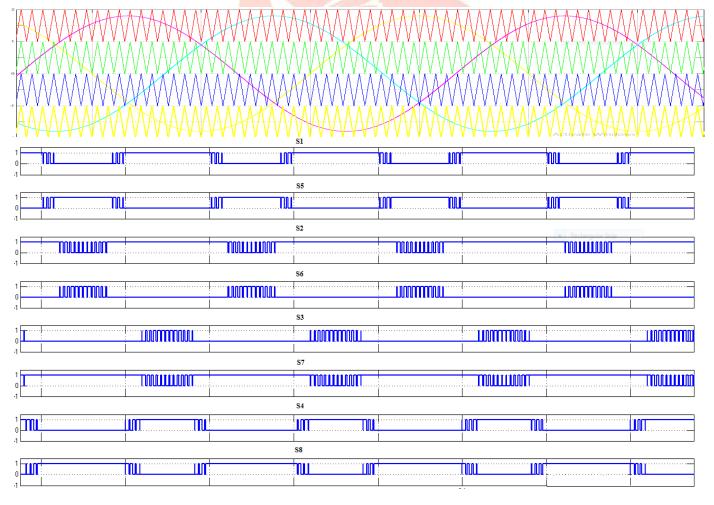

Fig. 8. shows the PWM circuit to generate the gating signals for the multilevel inverter switches. To control a three phase multilevel inverter with an output voltage of five levels; four carriers are generated and compared at each time to a set of three sinusoidal reference waveforms. One carrier wave above the zero reference and one carrier wave below the reference and the other one have 2 as amplitude and the other has -2. These carriers are same in frequency, amplitude and phases; but they are just different in dc offset to occupy contiguous bands. Phase disposition technique has less harmonic distortion on line voltages.

Fig.8. PWM simulation circuit

Fig.9. shows the waveform of sine-triangle intersection. Two carriers together with modulation signal have been used to obtain SPWM control.

Fig.9. Gate pulses for one leg switches

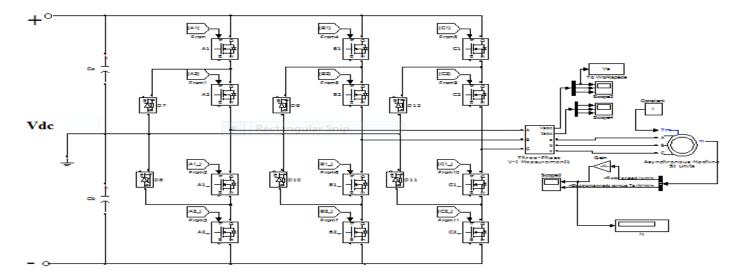

Simulated model for entire circuit is shown in Fig.10

Fig.10. Simulated circuit

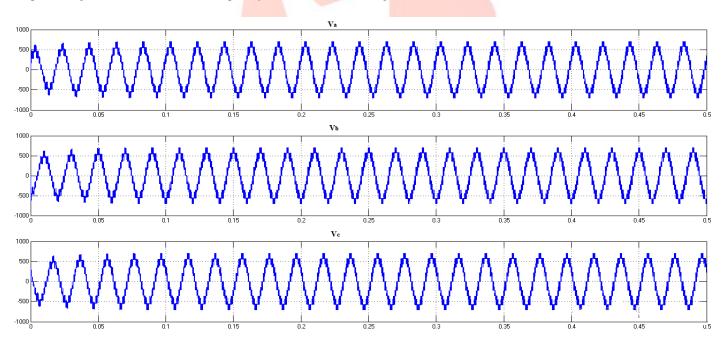

Output voltage waveforms for 50 Hz frequency are shown in below figure 11

Fig.11. Output line-line voltage for 50 Hz frequency

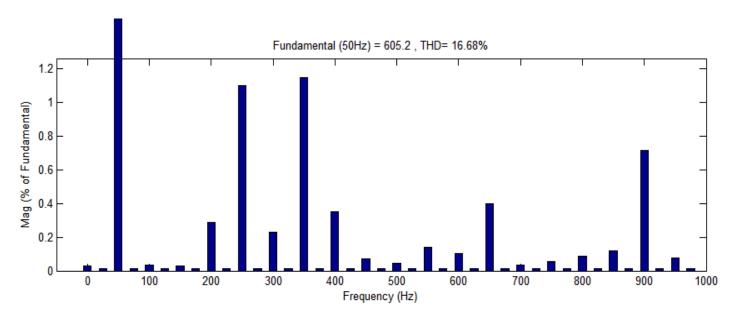

The FFT plot of the output voltage is shown in Fig. 12. The plot shows that the harmonic content present in the output voltage is very low. The frequency of reference signal determines the inverter output frequency; and its peak amplitude controls the modulation index. The variation in modulation index changes the rms output voltage of the multilevel inverter. By varying the reference signal frequency as well as modulation index, the speed of an induction motor gets controlled.

Fig.12. FFT for output voltage

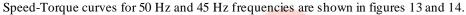

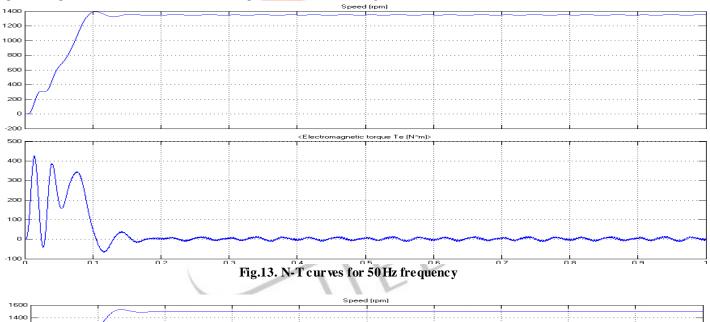

Fig.14. N-T curves for 45 Hz frequency

The speed-torque curves conclude that the voltage and frequency applied to the motor gets decreased; then the speed of an induction motor also decreased simultaneously.

TABLE 2: Speed range for different MI and frequency values.

| MODULATION                 | EDEO HENGY       | FIVE-LEVEL INVERTER |         |       |  |  |

|----------------------------|------------------|---------------------|---------|-------|--|--|

| MO DULATIO N<br>INDEX (MI) | FREQ UENC Y (Hz) | Time<br>(sec)       | N (rpm) | THD%  |  |  |

| 0.9                        | 50               | 0.16                | 1499    | 16.5  |  |  |

| 0.81                       | 45               | 0.18                | 1351    | 24.74 |  |  |

| 0.75                       | 40               | 0.22                | 1200    | 37.02 |  |  |

| 0.65                       | 35               | 0.25                | 1049    | 51.33 |  |  |

| 0.55                       | 30               | 0.25                | 892     | 95.45 |  |  |

### CONCLUSION

In this paper a diode clamped multilevel inverter has been presented for drive applications. The multicarrier PWM technique can be implemented for producing low harmonic contents in the output, hence the high quality output voltage was obtained. The open loop speed control was achieved by maintaining V/f ratio at constant value. The simulation results show that the proposed system effectively controls the motor speed and enhances the drive performance through reduction in total harmonic distortion (THD). This drive system can be used for variable speed applications like conveyors, rolling mills, printing machines, Blowers and fans, Textile machinery and Crushers, Electric vehicle drives etc.

## REFERENCE

- [1] Jose, Steffen Sernet, Bin Wu, Jorge and Samir Kouro, "Multilevel Voltage Source Converter Topologies for

- Industrial Medium Voltage Drives," *IEEE Trans on Industrial Electronics*, vol.54, no.6, Dec 2007.

Dr.Rama Reddy and G.Pandian, "Implementation of Multilevel inverter fed Induction motor Drive," *Journal of* Industrial Technology, vol 24, no. 1, April 2008.

- [3] Nikolaus P. Schibli, T. Nguyen, and Alfred C. Rufer, "AThree-Phase Multilevel Converter for High Power Induction Motors," IEEE Trans on Power Electronics, vol.13, no.5, Sept 1998.

- [4] N.Celanovic and D.Boroyevich, "A Comprehensive study of neutral-point voltage balancing problem in three level neutral - point- clamped voltage source PWM inverters," IEEE Trans on Power Electronics, vol.15, no. 2, pp. 242 – 249, March 2000. pp. 1098-1107, Sept. 1999. 5. Leon M. Tolbert, Fang Zheng Peng and Thomas G. Habetler, "Multilevel PWM methods at Low modulation Indices," IEEE Trans on Power Electronics, vol.15, no.4, July 2000.

- [5] N.S. Choi, J.G.Cho, and G.H.Cho, "A general Circuit topology of multilevel inverter," in Proc. IEEE PESC'91, 1991, pp.96-103.

- [6] Jae Hyeong Seo, Chang Choi and Dong Seok,"A New Simplified Space-Vector PWM Method For Three- Level Inverters," IEEE Trans on Power Electronics, vol.16, no. 4, July 2000.